Technical Program

NOTE: Oral presentation are scheduled as 20 MINUTES plus 5 MINUTES for questions.

Wednesday 26

| 08:00 | Registration |

| 09:00 | SPL 2008 Inauguration and Plenary Conference 1 : "Actel FPGAs for High Reliability Applications", Ken O’Neill,

Director, Military and Aerospace Product Marketing,

Actel Corporation. |

| 10:00 | Poster Session 1 / Coffee break |

| 11:00 | Session W1: DSP, Chairperson: Valentin Obac Roda FPGA-Based Architecture for Robust Optical Flow Computation Implementation of a FFT/IFFT module on FPGA: Comparison of Methodologies FPGA Implementations of an Adaptive Noise Canceller for Robust Speech Enhancement Interfaces |

| 12:15 | Lunch |

| 14:00 | Session W2: Aerospace and Applications, Chairperson: Guillermo Jaquenod FPGA-Based Transmit/Receive Distributed Controllerfor the TR Modules of an L Band Antena (SAR) Design of a Coherent Generation and Acquisition System at 1,2GHz Hazard-Free Implementation of the Extended Burst-Mode Asynchronous Controllers in Look-up Table Based FPGA A Low Cost FPGA-Based USB Device Core |

| 15:40 | Coffee break |

| 16:00 | Session W3: Physical Design, Chairperson: Guillermo Güichal A digital PLL Circuit for AC Power Lines with Instantaneous Sine and Cosine Computation Energy Evaluation in the NIOS II Processor as a Function of Cache Sizes The Coarse-Grained/Fine Grained Logic Interfece with Embedded Floating-Point Arithmetic Units Design and Implementation of FDP FPGA |

| 17:40 | End of sessions |

| 17:45 | INVAP visit: Institutional and technical presentation, and snack. |

Thursday 27

| 08:30 | Plenary Conference 2: "The Promises and Challenges of High-performance Reconfigurable Computing",

Sergio Lopez-Buedo, NSF Center for High-Performance Reconfigurable Computing / UAM. |

| 09:20 | Poster Session 2 / Coffee break |

| 10:20 | Session T1: Hw-Sw Co-Design & High-Level Languages, Chairperson: José I. Martínez Torre Simulation-based Approach for Evaluating Network-on-Chip Interconnect Architectures Polynomic curve based representation system implemented using FPGAs A VLSI architecture suitable for Mid-Level Image Processing Function Call Optimisation in SystemC Hardware Compilation |

12:00 |

Lunch |

| 13:45 | Session T2: Reconfiguration, Chairperson: Carlos Valderrama Aerodynamics Analysis Acceleration Through Reconfigurable Hardware On the Reconfiguration Costs of Models for Partially Reconfigurable FPGAs Reconfigurable Architecture for Embedding Web Services A Reconfigurable Prototyping Platform for Smart Sensor Networks |

| 15:25 | |

| 16:15 | Session T3: Computer Arithmetic, Chairperson: Eduardo Boemo Elliptic-Curve Point-Multiplication Over GF(2163) Architectural Tradeoffs in the Design of Barrel Shifters for Reconfigurable Computing PGA-Based Acceleration of the Computations Involved in Transcranial Magnetic Stimulation |

| 17:30 | End of sessions |

| 19:00 |

Friday 28

| 9:00 | Session F1: Vision & Video, Chairperson: Victoria Rodellar FASTCAM: Real-Time Implementation of the Lucky Imaging Technique Using FPGA Power Savings in FPGA Video Compression Systems Through Intra Prediction Result Reuse The Advanced Correlation Tracker in Real-Time |

| 10:15 | |

| 11:15 | Concluding Remarks and Awards |

| 11:45 | Culture at SPL: Argentine Tango, a Dance Exhibition |

| 12:30 | End of Conference |

Wednesday 26th

Plenary Conference 1 (9:10 to 9:50)

Presentation Title: Actel FPGAs for High Reliability Applications

Speaker: Ken O’Neill, Director, Military and Aerospace Product Marketing, Actel Corporation.

Abstract:

Designers of high reliability applications, such as commercial avionics, military avionics, weapons systems, and space-flight systems, are faced with a challenge when selecting digital logic integrated circuits (ICs). Usually the key criteria for component selection include IC quality screening levels, longevity of supply, availability of reliability data, and a heritage of successful deployment. In today’s diminishing supplier base it is difficult to identify parts that meet these criteria while also meeting requirements for functionality. In addition, new reliability threats are emerging, such as the effects of background atmospheric radiation, and the challenges posed by each successive advance into deep submicron process technology. The effects of these threats must be understood by designers making component selections for high reliability applications. Actel has a range of FPGAs which offer the highest levels of screening for military and space applications, backed by exhaustive reliability testing. Parts are offered with screening levels suitable for commercial avionics, military systems, and space systems. In this presentation we review the Actel product line of military and space FPGAs, and examine the latest reliability and radiation test data.

Short Bio:

Ken O'Neill has held the position of Director of Military and Aerospace Product Marketing at Actel Corporation since September 2002. Prior to this position, he served as Director of Marketing for Bridge Products at Actel. O'Neill originally joined Actel in June 1990 as a Product Marketing Engineer and has held several marketing and field applications engineering positions. Before joining Actel, O'Neill served as a Design Engineer with Hewlett-Packard's Computer Peripherals Group. Prior to that, he was a Design Engineer with Racal-Comsec Ltd. O'Neill holds a Bachelor's degree in Electronics Engineering from the University of Reading, England.

Poster Session 1 (10:00-11:00)

43. A Vhdl Can Module for Smart Sensors

José Reges, Edval Santos

Universidade Federal de Pernambuco, Brazil

51. Automated Signature Insertion in Combinational Logic Patterns

Encarnacion Castillo, Luis Parrilla, Antonio García, Uwe Meyer-Baese, Guillermo Botella

University of Granada, Spain

57. An Implementation of Compact Genetic Algorithm on FPGA for Extrinsic Evolvable Hardware

Tiago Oliveira, Valfredo Pilla Jr

UnicenP - Centro Universitário Positivo, Brazil

81. TDES Implementation in a Reconfigurable Computing Enviroment

Jose Jaramillo-Villegas, Esteban Correa-Agudelo, Rene Gomez-Londoño

Universidad Tecnologica de Pereira, Colombia

47. Digital Data Processing Peripheral Design for an Embedded App. Based on the Microblaze Soft Core

Enrique Ostua, Julian Viejo, Manuel J. Bellido, Alejandro Muñoz, Jorge Juan

Universidad De Sevilla, Spain

59. A control unit for a motion detector based on histograms

Valentin Roda, Danilo Minhoni

Universidade de São Paulo, Brazil

36. Hw Architecture for FPGA Implementation of a Neural Network and its App. in Images Processing

Leiner Barba, Lorena Paola Vargas, Cesar Torres, Lorenzo Mattos

Universidad Popular del Cesar, Colombia

45. A Complete Emulation System for Single Event Effects Analysis

Javier Napoles, Hipolito Guzman-Miranda, Miguel Aguirre, Jon Tombs, Juan Manuel Mogollon

University of Seville, Spain

Yuet Ming Lam, Jose Gabriel F. Coutinho, Wayne Luk, Philip Heng Wai Leong

Imperial College London, UK, The Chinese University of Hong Kong, China

22. Synthesis of Low-Power Synchronous Controllers Using FPGA Implementation

Duarte Oliveira, Alexis Salazar, Leonardo Romano

Instituto Tecnológico de Aeronáutica, Brazil

Visit to the new INVAP Headquarters

Date and Time: March 27, 2008, 17:45-20:00

A 40-minutes institutional presentation will be made at the Conference Venue. After that buses going to INVAP facilities will leave from the Conference Venue (Nevada Hotel) at 18:25.

The visit will include a tour to the EICO and EISA buildings facilities, where satellites and radar electronics systems are being integrated. Buses back to the Hotel Nevada will depart at 19:45.

A snack will be served at Hotel Nevada at 20:00.

Venue: Conference Venue and EICO Building (INVAP headquarters)

Thursday 27th

Plenary Conference 2 (8:30 to 9:10)

Presentation Title: The Promises and Challenges of High-performance Reconfigurable Computing

Speaker: Sergio Lopez-Buedo, NSF Center for High-Performance Reconfigurable Computing / UAM

Abstract:

The concept of High-Performance Reconfigurable Computing appeared some years ago. FPGA-based hardware acceleration is combined with conventional HPC parallelization techniques in order to maximize algorithm speedup. HPRC brings scalability to reconfigurable computing, as it enables many FPGA-accelerated nodes to work in parallel in order to increase performance. Nowadays, vendors like SRC, SGI or Cray offer powerful systems, and other companies such as IBM or HP are planning to offer their own systems. This talk will present an outlook of the current systems and development tools, and will also show some application examples illustrating the potentials of HPRC. However, there is still much work to be done in order for HPRC to become a mainstream technology, mainly regarding tools. This talk will present what are the challenges of HPRC, and how this challenges are being tackled at CHREC, the NSF Center for High-Performance Reconfigurable Computing.

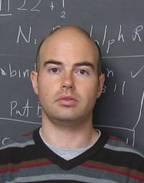

Short Bio:

Sergio Lopez-Buedo received in 2003 his Ph.D. in Computer Engineering from Universidad Autonoma de

Madrid ( Spain ), where he currently holds an associate professor position in the area of Computer Architecture. He also collaborates with the Universita degli Studi de Trento ( Italy ) as a consulting professor, and as a faculty member of the NSF Center of High Performance Reconfigurable Computing at The George Washington University (USA). FPGA technology is his main research interest, especially low-power, high-speed design, self-reconfiguration, high-performance reconfigurable computing and communication applications. Dr. Lopez-Buedo holds more than 50 publications, including journals, conferences and books as editor.

Sergio Lopez-Buedo received in 2003 his Ph.D. in Computer Engineering from Universidad Autonoma de

Madrid ( Spain ), where he currently holds an associate professor position in the area of Computer Architecture. He also collaborates with the Universita degli Studi de Trento ( Italy ) as a consulting professor, and as a faculty member of the NSF Center of High Performance Reconfigurable Computing at The George Washington University (USA). FPGA technology is his main research interest, especially low-power, high-speed design, self-reconfiguration, high-performance reconfigurable computing and communication applications. Dr. Lopez-Buedo holds more than 50 publications, including journals, conferences and books as editor.

Poster Session 2 (09:20-10:20)

38. Optimizing Reconfigurable Hardware for Genomic Sequences Comparison

Juan Jose Marfil, Daniel Mozos

Universidad Complutense de Madrid, Spain

42. Area Optimization of Combined Integer and Floating Point Circuits in High-Level Synthesis

Esther Andres Perez, M. C. Molina Prego, G. Botella Juan, A. del Barrio García, J. M. Mendías Cuadros

Complutense University of Madrid, Spain

68. Real Time FPGA Based Thresholding Segmentation in A Multi Touch System

Fernando Szklanny, E. Gho, Carlos E. Maidana, C. A. Rodríguez, Elio A. De María, Hugo R. Tantignone

Universidad Nacional de La Matanza, Argentina

80. Design and Implementation of Reconfigurable OFDM Modulator for Software-Defined Radios

Oscar Robles, Carlos Silva

Pontificia Universidad Católica del Perú

27. Parallel Implementation of the Shortest Path Algorithm on FPGA

Ivan Fernandez, Javier Castillo, Carlos Sanchez, Cesar Pedraza, Jose Ignacio Martinez

Universidad Rey Juan Carlos, Spain

40. Development Tools for Partial Reconfigurable Systems

Filippo Valiante Filho, Edson Lemos Horta

Universidade de São Paulo, Brazil

53. SSDR - Reconfigurable Firewall: Reconfiguration Model Performance

Fábio Pereira, Edward David Moreno Ordonez

USP-University of São Paulo, Benq-Siemens, Brazil

58. FPGA Based Multi-Harmonic Control System for Single Bubble Sonoluminescence

Damián Dellavale, Maximiliano Sonnaillon, Fabián Bonetto

Balseiro Institute, Argentina

91. An Image Processing Architecture to Exploit I/O Bandwidth on Reconfigurable Computers

Miaoqing Huang, Olivier Serres, Sergio Lopez-Buedo, Tarek El-Ghazawi, Greg Newby

The George Washington University, University of Alaska Fairbanks, USA

93. FPGA Hardening Through Built-In Dynamical Reconfiguration and Xtmr Techniques

Alberto Martin-Ortega, Sergio Lopez-Buedo, Santiago Rodriguez, Maite Alvarez, Sergio Esteve

Instituto Nacional De Tecnica Aeroespacial, Spain

54. Iddt Test Calibration Using a Programmable Processing Array

Mikhail Itskovich, James Plusquellic

University of Maryland Baltimore County, USA

Designer Forum 1 (15:40-16:40)

94. Implementación en FPGA de un Generador de Ruido Coloreado

Omar G. Zabaleta, Luciana De Micco, Claudio M. González, Constancio M. Arizmendi, Hilda A. Larrondo

Universidad Nacional de Mar del Plata, Argentina

29. Sniffer USB 2.0 (Full Speed)

Julián Bruno, Jerónimo Atencio, Pablo Gómez Martino

Universidad Tecnológica Nacional, Argentina

76. Métodos de Medición y Análisis del Contenido Armónico en Señales Eléctricas

Jorge Naguil, Esteban Pereyra Toledo, Walter Coba

Instituto Universitario Aeronautico,

U.T.N.,

Argentina

75. Motor de Protocolo para Capa de Protcolo USB 2.0

Diego Esteban Costa, Esteban Maximiliano Pelaez, Carlos Sosa Paez, Hector Gellon

Universidad Nacional de San Luis, Argentina

86. Implementación en FPGA de una función exponencial en punto fijo

Alejandro M. Boeri, Claudio M. González, Hilda A. Larrondo

Universidad Nacional de Mar del Plata, Argentina

5. Redes Inalámbricas de Sensores Inteligentes: Implementación con FPFA de un Algoritmo de Establecimiento del Árbol de Encaminamiento

Rosa Marina Corti, Roberto Manuel Martínez, Estela D´Agostino, Enrique Esteban Giandomenico

Universidad Nacional de Rosario, Argentina

70. Serviço de Gerenciamento de Dispositivos de Borda Reconfiguráveis em um Ambiente Pervasivo

Eduardo da Silva Möller, Wagner Al-Alam, Maurício Lima Pilla, Adenauer Corrêa Yamin

Universidade Católica de Pelotas, Brasil

28. FPGA based Real Time Non Linear Image Processor

Emerson Pedrino, Valentin Roda, Osmar Ogashawara

Universidade de São Paulo, Brasil

74. Algoritmo para Detección de Parásitos en la Sangre

Daniel Hoyos, Maiver Villena, Victor Serrano

Universidad Nacional de Salta, Argentina

72. Logical-Binary Functions Using Mos Floating-Gate Devices

Alejandro Medina Santiago, Mario Alfredo Reyes Barranca

CINVESTAV-IPN, Mexico

Friday 28th

Designer Forum 2 (9:20-10:20)

73. Sistema de Instrumentacion Remota en UAVs usando Linux sobre FPGA

Jose Jaramillo-Villegas, Lina Perez-Perez, John Osorio-Rios

Universidad Tecnologica de Pereira, Colombia

52. Controlador De Memoria DDR Configurable con Interfaz Wishbone

Federico Paredes, Darío Chans, Esteban Pereyra Toledo

Universidad Tecnológica Nacional, Argentina

88. A FPGA Implementation for Classification Using Digital Rotation Support Vectors Machines

Horacio Lamela, Matías Jimenez, Gimeno Jesús, Marta Ruiz

Universidad Carlos III de Madrid, Spain

61. Implementación en FPGA del algoritmo ADM para detección de bordes

Maximiliano Sacco, Patricia Borensztejn

Universidad de Buenos Aires, Argentina

4. Interfaz de depuración para microcontrolador

Salvador Tropea

Instituto Nacional de Tecnología Industrial, Argentina

77. Evaluating Fault-Tolerant Fast Adders Implemented in FPGAs

Guilherme Corrêa, Eduardo Mesquita, Helen Franck, Luciano Agostini, José Luís Güntzel

Universidade Federal de Pelotas, Universidade Federal de Santa Catarina, Brasil

18. Pipeline-Based Power Reduction in FPGA Applications

Miguel A. Sacristan, Victoria Rodellar, Antonio Diaz

Universidad Politecnica de Madrid, Spain

13. Ethernet Communication Block

Maria Isabel Schiavon, Daniel Crepaldo, Raul Lisandro Martin, Carlos Varela

Universidad Nacional de Rosario, Argentina

56. PDA Based on Altera Nios Ii Processor and Uclinux Operation System Embedded in FPGA

Roberto S. Junqueira, Valfredo Pilla Jr

Centro Universitário Positivo, Brasil

20. MIL-STD-1553B Bus Monitor

Felipe Pasquevich, Mauricio Lange

CONAE, Argentina

Culture at SPL: Argentine Tango, a Dance Exhibition (11:45)

Pablo Contreras and Cinthya Palacios, coming from General Roca, Rio Negro, and very talented dancers, will perform Argentine Tango at the end of the Conference.

Last Update 25.03.2008